◆ コンパレータ は、2 つの入力電圧の大小関係を判定し、その結果を、1 か 0 かのディジタルで出力する IC です(図.1)。

◆ 動作原理や回路構成は、ほとんどオペアンプと同じです。オペアンプ IC をフィードバックを掛けずに、オープンで使用すれば、コンパレータとして動作します。しかし、専用のコンパレータ IC を使用する方が、より良い特性が得られます(とくに高速を要する場合)。

コンパレータは、入力がアナログ、出力がディジタルです。1 ビットの A/D (アナログ/ディジタル)変換器と考えることができます。

コンパレータ IC の出力は、オープンコレクタ (TTL)、またはオープンドレイン (C-MOS)のものがあります(図.2)。オープンドレインは、機能的には、オープンコレクタと同じで、素子が C-MOS のものです。

◆ アナログ系とディジタル系とで、電源電圧が異なることが、あります。図に示すように、IC の電源電圧と異なる電圧で、ディジタル出力をプルアップすることによって、アナログ系とディジタル系の電圧を変えることができます。

[注] 一般のディジタル IC の出力は、模型的に示すと図(a)、(b)に示すように、2 個のスイッチのオンオフによって、信号レベルがローかハイになります。これに対してオープンコレクタ/オープンドレインは(c)に示すように示すように、スイッチが 1 個なので、単独では出力レベルは変化しません。図.2 に示すように、プルアップ抵抗を外付けすることによって、スイッチのオンオフにより出力が、ロー/ハイに変化します。

◆ コンパレータは、感度が高いことが特徴です。しかし、それなるが故に、ノイズには弱いのです。

コンパレータは、発振し易いと言われています。一見発振のような現象ですが、いわゆる発振ではありません。低周波の信号に,高周波の僅かなノイズが載っても、そのノイズによってコンパレータが正常に動作します。その結果として、コンパレータの出力が、ハイ/ローを繰り返します。それが発振のように見えるのです。

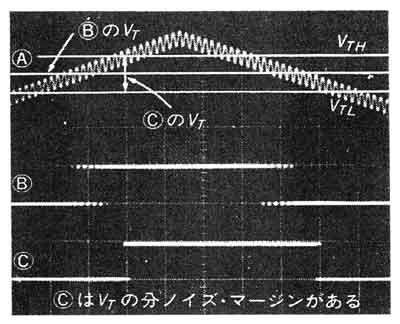

この現象を、無くすためには、シュミットトリガ特性(ヒステリシス)を持たせます。図.3 は、この現象を分かりやすく示すための実験回路、図.4 は、その実験波形です。

◆ 図.3 において、上側のコンパレータ回路は、ノイズ対策を施さない回路です。下側のコンパレータは、シュミットトリガ特性を持たせることによって、ノイズ対策を行った回路です。

両回路とも、コンパレータのマイナス側の入力を一定(電圧 VT)とし、プラス側に高周波のノイズが重畳した波形(A)を加えます。

(B)は無対策側の出力です。(A)の電圧が、上昇(または下降)する際に、ノイズがあるために、スレッショルド電圧 VT を何度か切ります。その度にコンパレータが正常に動作して、あたかも、発振であるかのように、出力電圧(B)がハイ/ローを繰り返します。

◆ 下側の回路は、ノイズ対策として、コンパレータに、シュミットトリガ特性を持たせた回路で、その出力は(C)です。出力のバタツキは、ありません。

シュミットトリガ特性は、正のフィードバック回路によって作ります。20kΩ の入力抵抗と、100kΩ のフィードバック抵抗が、シュミットトリガ特性を、作る回路です。

ヒステリシス特性は、スレッショルドレベルを 2 つ(VTHとVTL)持っています。(A)の電圧が上昇するときは VTH、下降するときは VTL で動作します。この結果図に示すように、出力(C)は、(A)の上昇時と下降時に、各 1 回だけ動作します。

◆ 図.5 は、シュミットトリガ特性のスレッショルドレベルの値を示す図です。

◆ シュミットトリガ特性を持たせることによって、ノイズによる発振的な現象を防ぐことができますが、当然の結果として、ヒステリシス幅だけ、コンパレータの感度が低下します。したがって、ヒステリシス幅は、予想されるノイズの大きさに対して、十分であることは必要ですが、大きすぎることは避けなければなりません。

★ コンパレータは、比較器です。いろいろなものを比較してみるのは、楽しいものです。とくに、駅弁の比較ともなれば、その楽しさは、倍増です。

★ 新幹線の開通によって、横川駅の、峠の釜飯は無くなりましたが、代わりに、高速のサービスエリアで売っています。左下は、昔の横川駅のものです。

★ 右上は、コンパレータ回路の一例です。

コンパレータ応用回路の代表的なものに、ウィンドウコンパレータがあります。ウィンドウコンパレータは、電圧が、特定の電圧範囲の中に収まっているかどうかを、調べる回路です。ウィンドウコンパレータは、コンパレータを 2 個使って、電圧 Vin が、上限値 VU と、下限値 VL の間に入っているかどうかをチェックします。